Cx Language

Hardware description that doesn't require a PhD. C-like syntax meets hardware semantics. Write concurrent, parallel systems using the programming model you already know.

Why Cx exists

Verilog was designed in 1984. VHDL in 1983. They were revolutionary for their time. But modern software development has learned a lot in 40 years about readable code, type systems, and tooling.

HDLs force you to think at the wire level. Cx lets you think at the architecture level. You describe what your hardware does, not how every signal toggles.

This is not High-Level Synthesis (HLS). HLS tools are black boxes that generate RTL you can't understand or debug. Cx compiles to clean, readable Verilog/VHDL at the right level of abstraction—code you can actually read, review, and understand.

Result: Code that's easier to write, easier to read, easier to maintain—and compiles to transparent HDL you'd be happy to write by hand.

See the difference

Cx (What you write)

// Simple UART transmitter

task uart_tx {

in sync u8 data;

out bit tx;

const u32 BAUD = 115200;

const u32 CLK_FREQ = 50_000_000;

void main() {

tx = 1; // Idle high

while (true) {

u8 byte = data.read();

tx = 0; // Start bit

wait(CLK_FREQ / BAUD);

for (u8 i = 0; i < 8; i++) {

tx = byte[i];

wait(CLK_FREQ / BAUD);

}

tx = 1; // Stop bit

wait(CLK_FREQ / BAUD);

}

}

}Verilog (What you'd write)

// Equivalent Verilog module uart_tx ( input wire clk, input wire rst, input wire [7:0] data, input wire data_valid, output reg data_ready, output reg tx ); parameter BAUD = 115200; parameter CLK_FREQ = 50_000_000; reg [15:0] counter; reg [3:0] bit_idx; reg [7:0] shift_reg; reg [2:0] state; localparam IDLE = 0; localparam START = 1; localparam DATA = 2; localparam STOP = 3; // ... 50+ lines of state machine // and counter logic endmodule

Same functionality. Half the code. Infinitely more readable.

Core Features

C-Like Syntax

If you know C, you already know most of Cx. Familiar control flow, familiar operators, familiar structure. The learning curve is measured in hours, not months.

if (count > THRESHOLD) {

enable = true;

status = READY;

}Strong Typing

Bit-accurate types prevent width mismatches before synthesis. No more "why is this signal X?"

u8 byte_data;

u16 word_data;

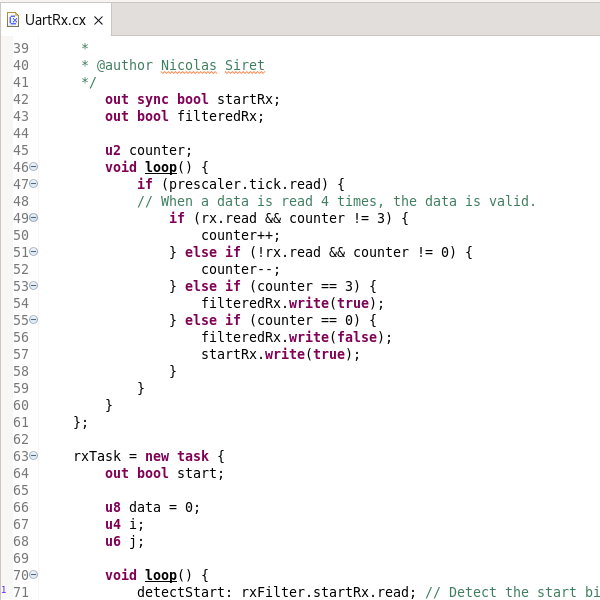

bool flag;Readable Concurrency

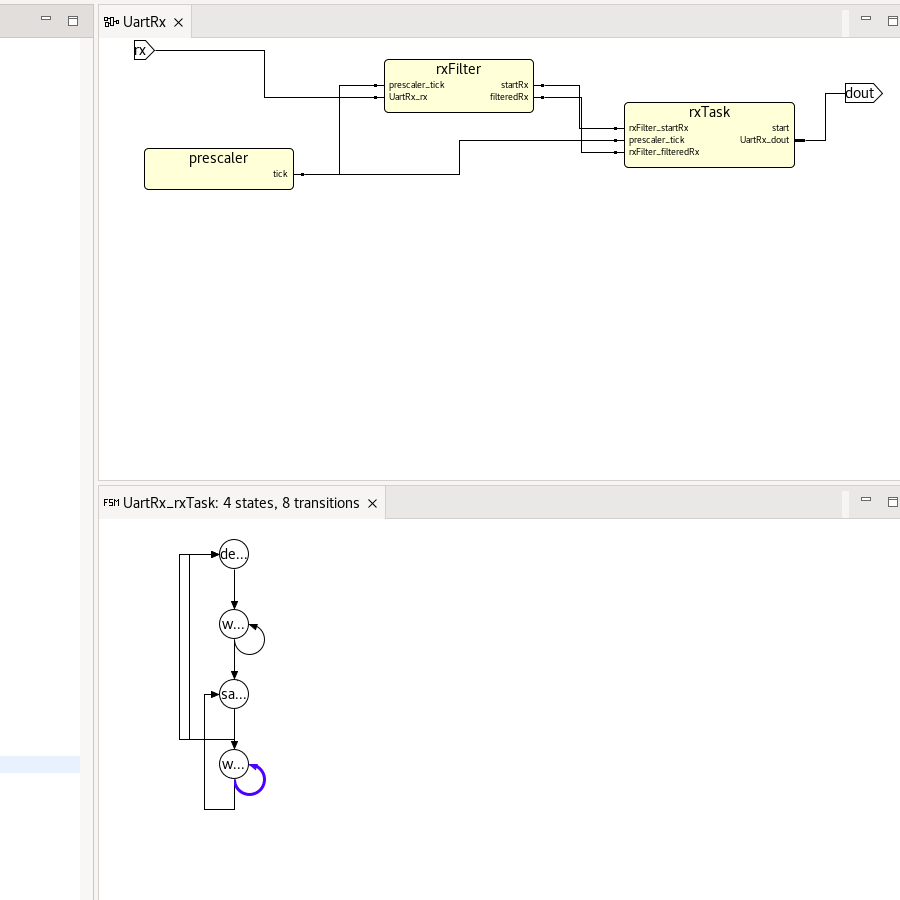

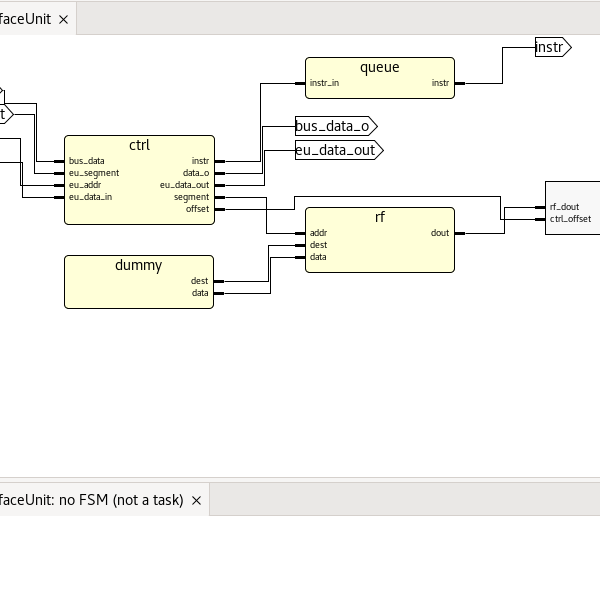

Tasks describe concurrent hardware naturally. Ports connect them. No sensitivity lists. No race conditions from typos.

in sync u8 input;

out sync u16 output;

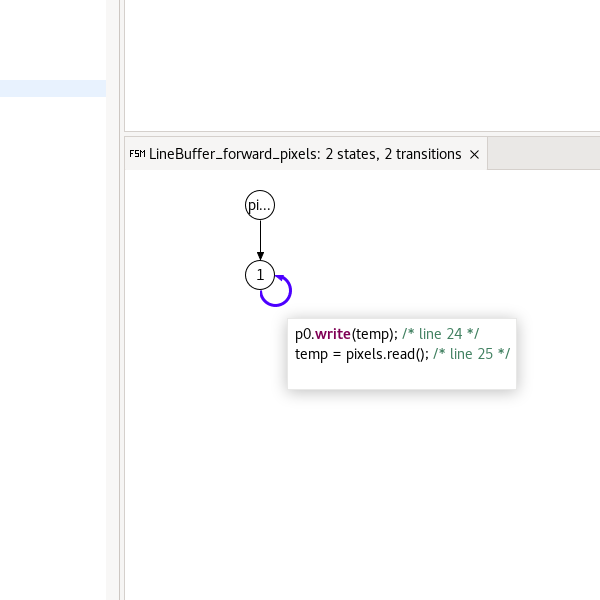

output.write(data);Built-in Hardware Constructs

FSMs, pipelines, and clock domain crossings are language primitives, not design patterns you reinvent every project.

wait(cycles);

sync_read(port);

clock_domain_cross(signal);In Practice

Clean, Maintainable Code

No more thousand-line case statements. No more searching for signal definitions across multiple modules. Cx code is structured like modern software—because readable code is debuggable code.

Type Safety at Hardware Scale

Bit-accurate types mean the compiler catches width mismatches, sign errors, and type incompatibilities. Find bugs at compile time instead of in simulation or—worse—on silicon.

Cycle-Accurate, Naturally

Express timing requirements explicitly with wait() calls. The compiler handles the state machines. You focus on the algorithm. Cycle-accurate behavior without the boilerplate.

IDE Integration That Works

Code completion. Jump to definition. Refactoring tools. All the IDE features you expect from modern development—because Cx code has the structure to support them.

Concurrency Without Chaos

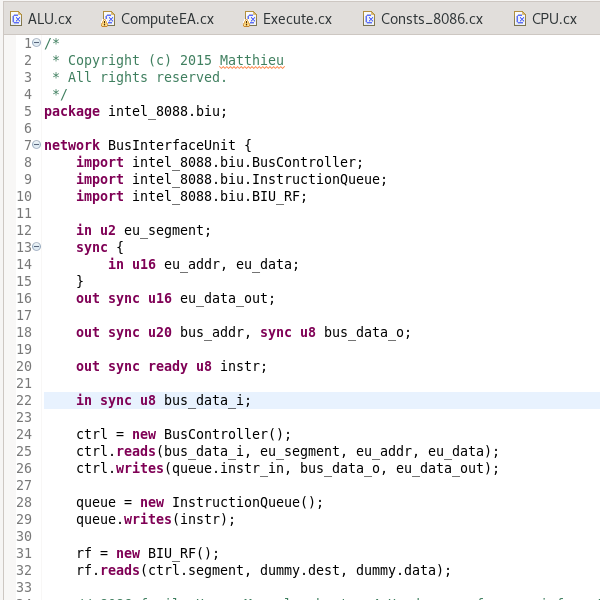

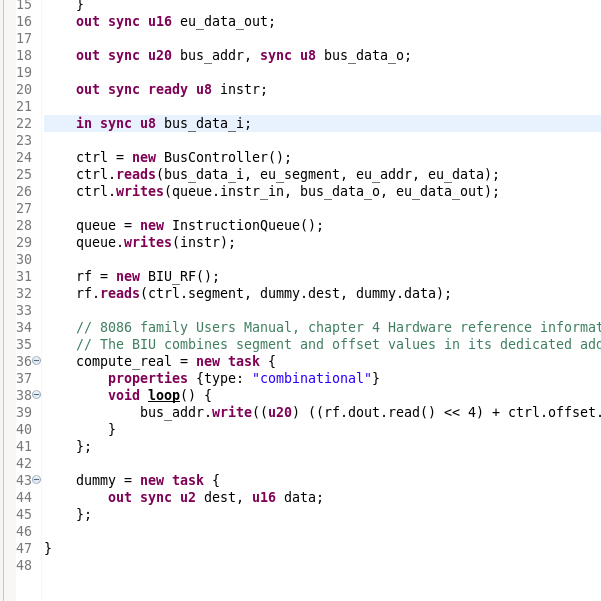

Tasks execute in parallel. Ports manage communication. Synchronous and asynchronous channels handle data flow. Write concurrent systems without fighting the language.

Transparent Compilation, Not HLS Magic

Cx compiles to readable Verilog/VHDL at the right abstraction level. No black-box RTL you can't understand. The generated HDL is clean, reviewable, and debuggable—exactly what Verilog should have been.

Technical Details

Type System

Bit-accurate types: u8,u32,bit,bool. Custom width integers like u17 oru127. Static type checking catches errors at compile time, not after hours of simulation.

Concurrency Model

Tasks run concurrently. Ports handle communication. Synchronous and asynchronous channels built in. Express parallelism naturally without wrestling with always blocks and sensitivity lists.

Clock Domains

First-class clock domain support. Cross-domain communication that's safe by default. No more metastability bugs from forgetting a synchronizer. The compiler understands clock domains.

Transparent Compilation

Compiles to clean, readable Verilog or VHDL at the right level of abstraction. Unlike HLS black boxes, the generated HDL is something you can actually understand—review it, debug it, hand-tweak if needed, or integrate it into existing HDL flows. You always know what you're getting.

Start writing better hardware code

Download the SDK and try Cx on a real project. Full language reference and tutorials included.